TECY

Freiraum 2022: Collaborative Remote Laboratory Platform

TECY is a web-based platform that enables students to collaboratively learn and program FPGAs (Field-Programmable Gate Arrays) in a virtual lab environment. The platform addresses the challenge that FPGA hardware is difficult to share among multiple users and physical lab access is often limited. Through remote access, students can design, test, and verify FPGA systems from anywhere, bridging the gap between theoretical knowledge and practical application.

Intro Video for Students

Funding & Resources

This project was funded by the Freiraum 2022 program of Stiftung Innovation in der Hochschullehre. It is a collaboration between the Computer Science Education group and the Institute for Embedded Systems at the University of Siegen.

Technical Implementation

My role was the design and development of the Collaborative Remote Laboratory Platform. Next to my own implementations I also supervised a master project group implementing several features.

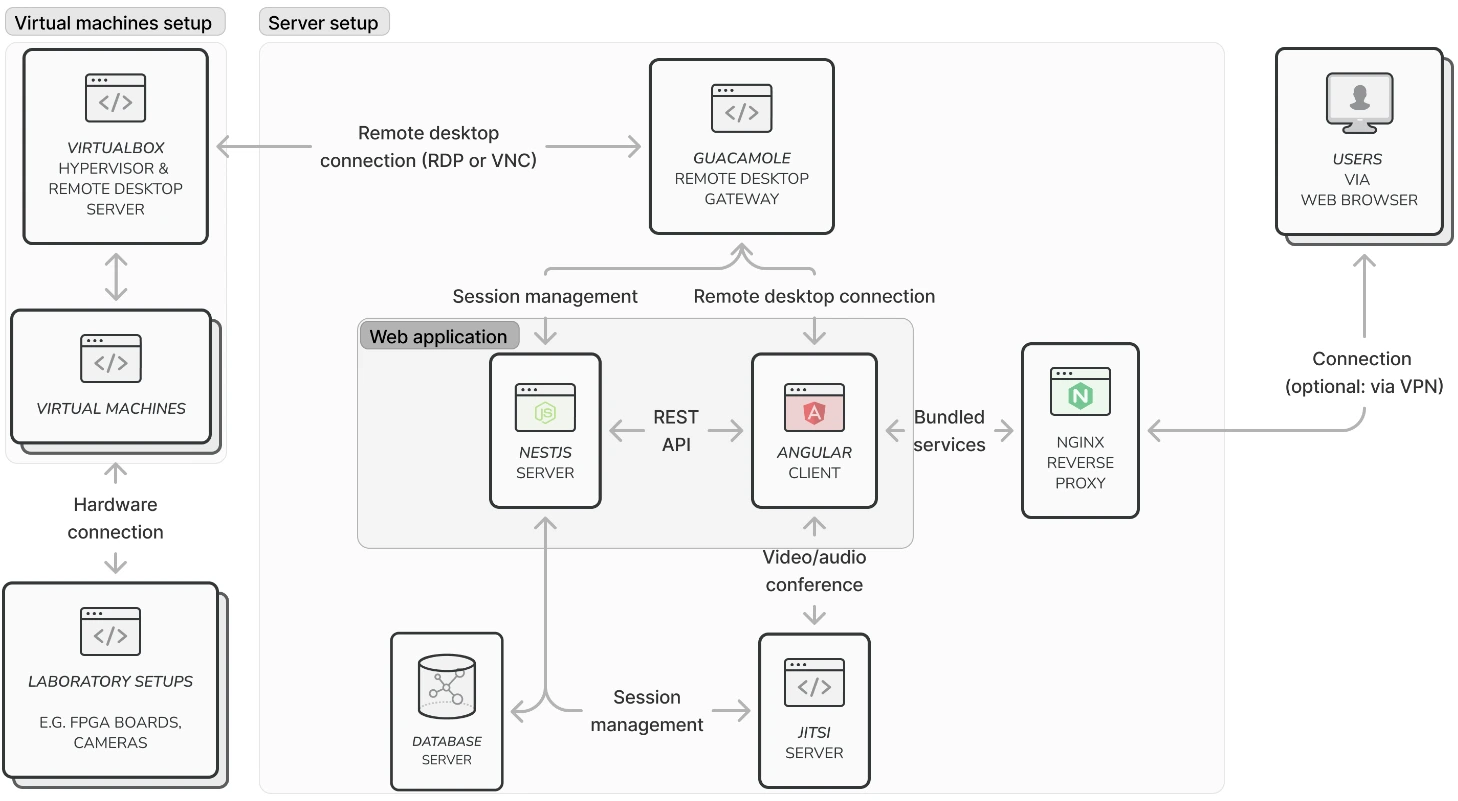

The platform consists of several integrated components:

- Web Application: Angular frontend with NestJS backend providing a central hub for all users

- Collaborative Workspace: Shared remote desktop sessions via Apache Guacamole where multiple students work together

- Video Conference: Integrated Jitsi instance for real-time audio/video communication

- FPGARLab Controller: Arduino-based system managing FPGA power, peripherals, and sensors

- Virtualization: Oracle VM VirtualBox hosting development environments with AMD Xilinx Vivado

Key Features

- 24/7 Remote Hardware Access: Students can access Xilinx Zynq FPGA boards (Zybo Z7, ZedBoard) anytime

- Collaborative Sessions: Multiple students share a common remote desktop, video conference, and chat

- Time Slot Booking: Self-service reservation system for fair resource allocation

- Real-Time Video Streaming: Live camera feed showing the physical FPGA board

- Hardware Debugging: JTAG interface for debugging, UART for communication

- Intelligent Power Management: Automatic light control and power-saving mode

- HDL Support: VHDL, Verilog, and SystemVerilog

Related Publications:

- Al Amin, R. A., Wiese, V., Rahman, M. M., Jacobs, S., Jaschke, S., & Obermaisser, R. (2023). Architecture of IoT-Based Collaborative Laboratory for Reconfigurable SoC: Review and Development. 2023 IEEE 2nd German Education Conference (GECon), 1-6. https://doi.org/10/gtx29s

- Jacobs, S., Hardebusch, T., Franke, E., Peters, H., Al Amin, R. A., Wiese, V., & Jaschke, S. (2024). Design and Development of a Multi-Purpose Collaborative Remote Laboratory Platform. 2024 IEEE Global Engineering Education Conference (EDUCON), 1-3. https://doi.org/10.1109/EDUCON60312.2024.10578743

- Amin, R. A., Wiese, V., Jacobs, S., Hardebusch, T., Jaschke, S., & Obermaisser, R. (2025). Requirement Analysis and Didactic Evaluation of a Collaborative Remote Laboratory for FPGAs. 2025 IEEE Global Engineering Education Conference (EDUCON), 1–5. https://doi.org/10.1109/EDUCON62633.2025.11016656